Call for Special Sessions

PDF Version

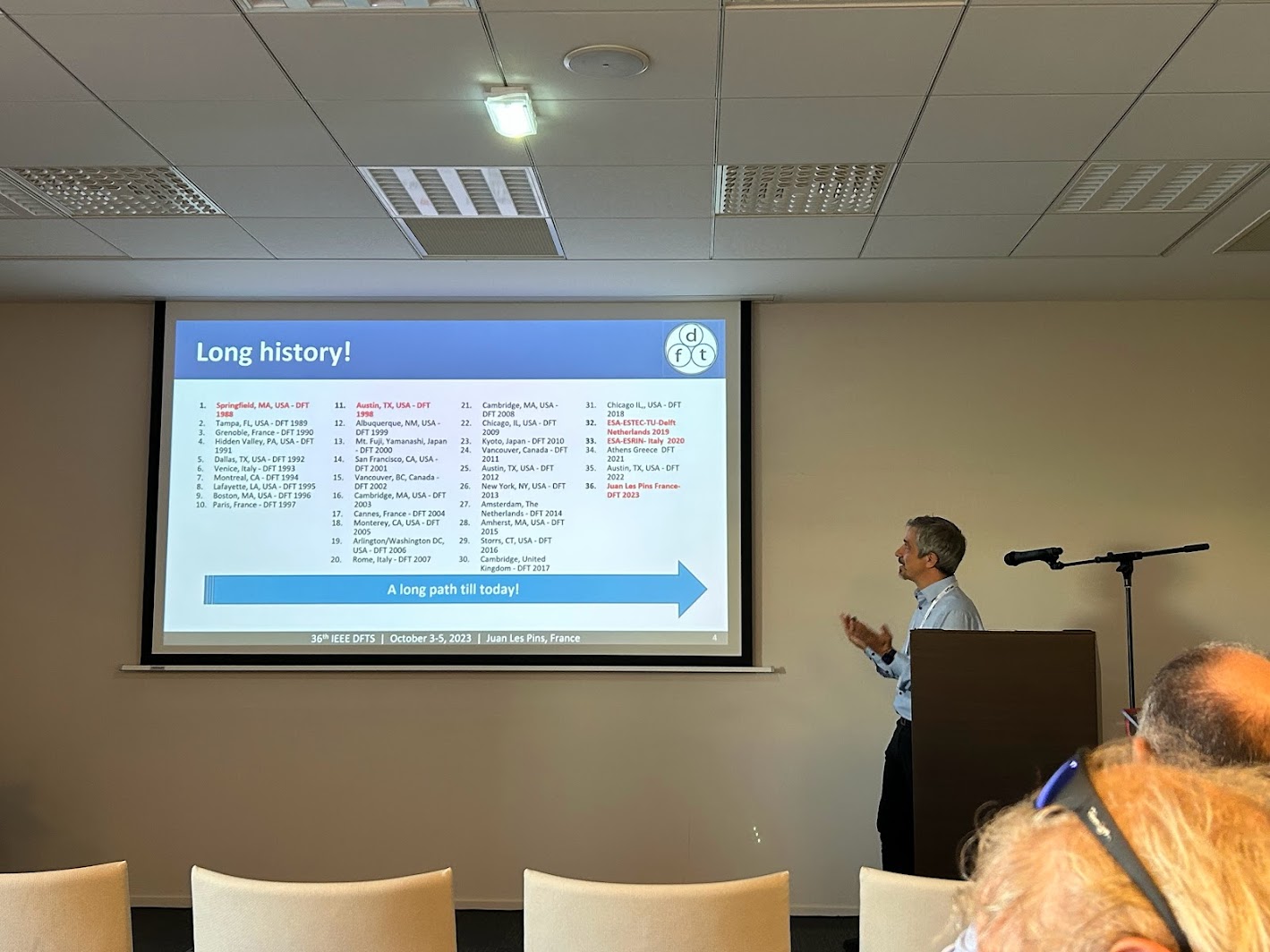

DFT’

seeks proposals

for Special Sessions. The special sessions should aim at

providing a complementary experience with respect to the

regular sessions by focusing on hot and emerging topics of

interest to the DFT community, as well as on multi-disciplinary

topics, that are expected to have a significant impact on DFT

activities in the future (e.g., reliability aspects in Machine

Learning, Approximate Computing, In-Memory Computing,

Neuromorphic-Computing, Quantum Computing, use of COTS

electronics for space applications, Hardened Microcontrollers,

RISC-V). A special session could consist of a set of individual

presentations, embedded tutorial or a panel,

possibly with experts from the industry.

Upon acceptance, special session presenters can prepare

one paper per speech

to be included in the formal proceedings.

For this reason, papers (presenting original and unpublished contributions and

that may be no longer than 6 pages, is possible to purchase 2 extra pages at an

additional cost) for special

session will go through review process

.

Accepted papers will appear in the formal proceedings of DFT

symposium. Proceedings will be published by the IEEE Computer Society

and will appear in the IEEE Explorer Digital Library

Submission Process: Submitted proposals should include:

-

a title of the special session

-

a maximum 250-word abstract outlining

the session's scope, topics and relevance for DFT symposium

-

name, contact information and short biography of the organizer(s)

-

format of the session: (1) panel or (2) individual presentations or (3) embedded tutorial; and

-

list of three/four contributed presentations

(including titles, presenter names, contact information of the corresponding presenter,

and an abstract of each contribution).

For panel proposals, list three to five panelists and their area of expertise.

For embedded tutorial, list three/four presenters and their short bio.

Proposal submissions should be presented in a single PDF to be sent via e-mail to the

Special Session Chair and for information to the Program Co-Chairs:

-

Luigi Dilillo - Special Session Chair - luigi.dilillo@umontpellier.fr

-

Luca Cassano - Program Co-Chair - luca.cassano@polimi.it

-

Mihalis Psarakis - Program Co-Chair - mpsarak@unipi.gr

-

E-mail Subject: DFT’

Special Session Proposal

By means of their submission,

all presenters

agree to register for and participate to

DFT’

, in case their special session

proposal is accepted.